FlexGen, a network-on-chip (NoC) interconnect IP, is aiming to accelerate SoC creation by leveraging AI.

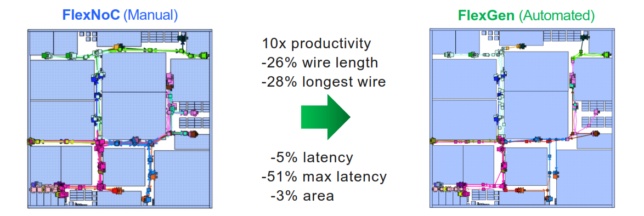

Developed by Arteris Inc., FlexGen promises to deliver a 10× productivity boost while reducing design iterations and the time required to develop.

Using AI and machine learning for chip design isn’t new, but often the productivity boosts come at the cost of performance or power.

FlexGen is based on Arteris’ FlexNoC 5 IP technology and component library and supports SoC and chiplet design automation based on Arm, RISC-V and x86 processors. AI enables the company to reduce manual adjustments by more than 90%, which means optimized NoC topologies can be generated in hours instead of days.

The industry has reached the point where manual NoC generation is beyond human capability, which is why AI and machine learning are needed to meet the complex designs that are being by driven by AI. Arteris quickly considered all the properties and requirements of all the IP blocks that were being connected to do develop the NoC generation.

One example of a customer that is benefiting from FlexGen is Dream Chip Technologies, which specializes in automotive AI used for advanced driver assistance systems (ADAS). FlexGen has enabled the company to create floorplan adaptive topologies with complex automotive traffic requirements within minutes.

FlexGen is just one of many examples of how AI is being used to boost productivity in semiconductor design. Digital twins have recently begun to take advantage of more sophisticated AI models, which allows them to be more accurate and allow for more experimentation. AI supports the development of foundation models that are relatively generic and can be added to with domain-specific and proprietary information.

The recent increase in chiplet adoption, meanwhile, has led to the growing need to accelerate analysis, design and deployment. Baya Systems’ algorithm-driven system architecture platform, WeaverPro, combined with its scalable IP and cache fabric, Weave IP, pulls together all the steps of building out chiplet architectures through data-driven design and optimization.

More recently, an update to the Arm Total Design initiative focuses on expanding the chiplet ecosystem with the launch of an AI/CPU chiplet platform that targets the cloud, high-performance computing and AI/ML training and inference workloads.

Read the full EE Times article.

Gary Hilson is a freelance writer with a focus on B2B technology, including information technology, cybersecurity, and semiconductors.