Better late than never might be a good way to sum up NRAM.

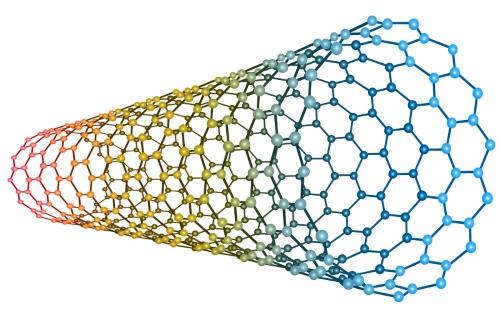

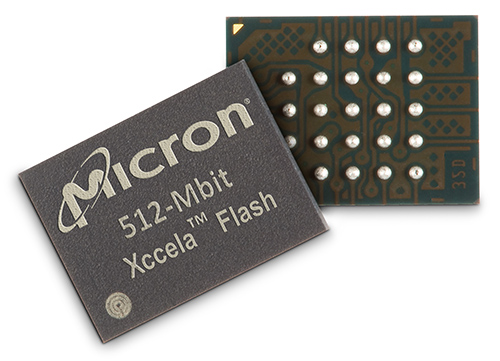

After years of not quite be ready for wide adoption, a new report from BCC Research is predicting that Nano-Ram (NRAM) is finally in a position to disrupt incumbent DRAM and flash memory with commercialization expected in 2018. The Wellesley, MA.-based research firm said the first non-volatile memory chip to exploit carbon-nanotube technology looks like it’s finally ready to have a serious impact on computer memory.

“Industry experts had given up on waiting for CNT memory,” said BCC Research editorial director Kevin Fitzgerald in an interview with EE Times. “I believe one needed fresh eyes to really see that the time was coming when it was really possible to make the switch from silicon to carbon.”