The latest point release to the Compute Express Link specification aims to optimize monitoring and management and enhance functionality for operating systems and applications—all while extending security.

The updates reflect the rapid growth of AI in the data center, even though the coherent connectivity protocol was conceived before the AI boom took off.

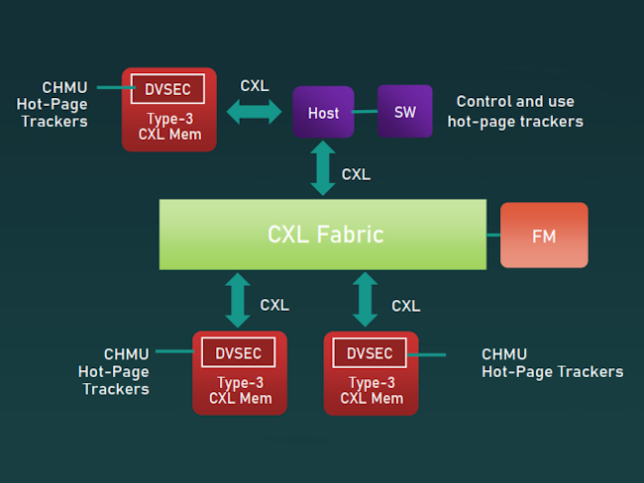

The latest CXL update, CXL 3.2, adds several monitoring and management capabilities, including a CXL hot-page monitoring unit (CHMU) for memory tiering, common event record, compatibility with PCIe management message pass through (MMPT) and CXL online firmware (FW) activation.

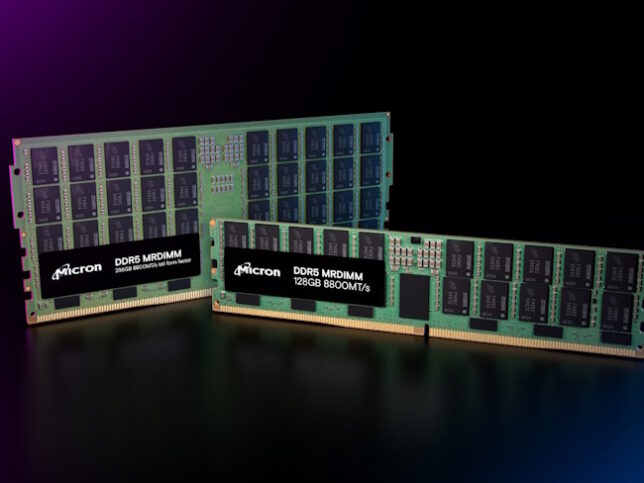

CHMU enables software to identify hot pages in second-tier memory and migrate them to first tier, such as DDR DRAM, to improve power and performance of the tiered memory solution. New common event record capabilities allow for improved granularity, monitoring precision and management of complex CXL device configurations, which enhances overall system performance and resource allocation.

Additional functionality in 3.2 includes post package repair (PPR) enhancements and performance monitoring events for CXL memory devices.

The trusted security protocol (TSP) features first introduced in CXL 3.1 are in line with confidential computing concepts pioneered by Intel that predate CXL and allow for virtualization-based trusted execution environments to host confidential computing workloads. Additional TSP features in 3.2 include IDE protection for late poison messages, which improves security for CXL-attached systems by allowing late poison messaging authentication using IDE.

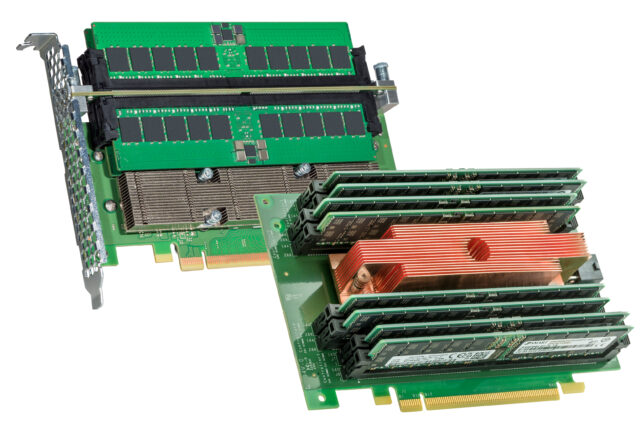

The CXL interconnect has evolved rapidly since its debut in 2019 with three sub-protocols: CXL.io, CXL.cache and CXL.memory. CXL.io is necessary for I/O instructions. The first iteration supported direct attachment of memory, while 2.0 added the capability to attach memory to a pool of processors, allowing for the use of storage-class memory or persistent memory, or tiers of memory with different performances and cost structures.

CXL 3.0 supports more disaggregation with advanced switching and fabric capabilities, efficient peer-to-peer communications, and fine-grained resource sharing across multiple compute domains.

Gary Hilson is a freelance writer with a focus on B2B technology, including information technology, cybersecurity, and semiconductors.