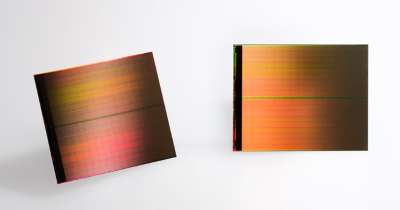

TORONTO — What the future holds for 3D XPoint — now that Intel and Micron have announced plans to end their joint development program — depends on who you talk to.

Or who you don’t talk to. Micron, for its part, isn’t offering any more guidance right now beyond what was stated in a joint news release issued earlier this week. “The companies have agreed to complete joint development for the second generation of 3D XPoint technology, which is expected to occur in the first half of 2019,” the statement reads. “Technology development beyond the second generation of 3D XPoint technology will be pursued independently by the two companies in order to optimize the technology for their respective product and business needs.”

Intel is still bullish on the technology. In a telephone interview with EE Times, Bill Leszinske, vice president of Intel’s non-volatile memory solutions group, said it makes sense for Intel to continue on its present path.

Gary Hilson is a freelance writer with a focus on B2B technology, including information technology, cybersecurity, and semiconductors.